半加法器HDL Verilog代码

本页verilog源代码里覆盖使用verilog的半加法器,半减法器,全减法器的HDL代码。

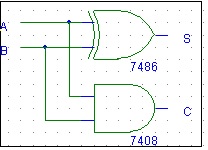

的一半加法器真值表和原理图(图1)如下所示。布尔表达式为:

S= a (exor) b

C =。B

| 输入一个 | Input-B | 信噪 | Output-C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

半加法器原理图

半Adder Verilog代码

模块ha (a, b, s, c)

输入a, b;

输出s, c;

赋值s= a ^ b;

赋值c= a & b;

终端模块

输入a, b;

输出s, c;

赋值s= a ^ b;

赋值c= a & b;

终端模块

一半Substractor

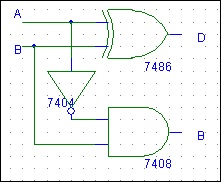

的一半substractor真值表和原理图(图2)如下所示。布尔表达式为:

D= a (exor) b

Br =“。B

| 输入一个 | Input-B | Output-D | Output-Br |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

半减子原理图

半减子Verilog代码

模块hs (a, b, d, br)

输入a, b;

输出d, br;

赋值d= a ^ b;

赋值br= ~a & b;

终端模块

输入a, b;

输出d, br;

赋值d= a ^ b;

赋值br= ~a & b;

终端模块

满Substractor

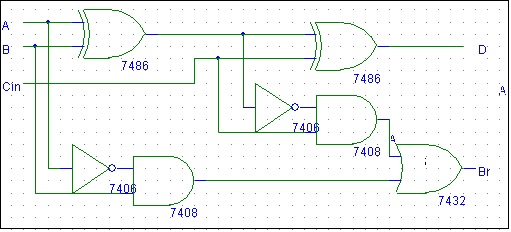

的满substractor真值表和原理图(图3)如下所示。布尔表达式为:

D= a (exor) b (exor) c

Br =“。B+ B.Cin + A'.Cin

| 输入一个 | Input-B | Input-Cin | Output-D | Output-Br |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

全减子原理图

完整的减分器Verilog代码

模块fs (a, b, c, d, br)

输入a, b, c;

输出d, br;

赋值d= a ^ b ^ c;

赋值br=(~a)& (b ^ c)) | (b & c);

终端模块

输入a, b, c;

输出d, br;

赋值d= a ^ b ^ c;

赋值br=(~a)& (b ^ c)) | (b & c);

终端模块

射频和无线教程

无线局域网802.11交流802.11广告wimax无线个域网z - waveGSMLTEUMTS蓝牙超宽频物联网卫星天线雷达