T D SR, JK触发器HDL Verilog代码

这个页面的verilog源代码里覆盖HDL代码T触发器,老D触发器,触发器和JK触发器用verilog。

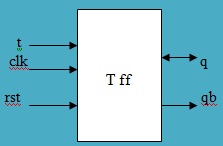

T触发器的象征

下面的符号和真值表T触发器。

T触发器真值表

| Rst | T | Clk | 问 |

|---|---|---|---|

| 1 | 0 | 1 | 问 |

| 1 | 1 | 1 | qb |

| 1 | X | 没有积极的边缘 | 以前的状态 |

| 0 | X | X | 0 |

T触发器Verilog代码

模块tff (t clk rst q qb);

输入t、clk rst;

输出q, qb;

qb reg问;

reg temp = 0;

always@ (posedge clk posedge rst)

开始

如果(rst = = 0)开始

如果(t = = 1)开始

temp = ~温度;

结束

其他的

temp = temp;

结束

q = temp; qb = ~温度;

结束

终端模块

仿真结果

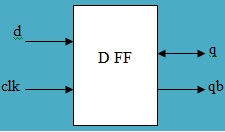

D触发器的象征

下面的符号和真值表D触发器。

D触发器真值表

| clk | d | 问 | qb |

|---|---|---|---|

| X | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

D触发器Verilog代码

模块dff (d, clk rst q qb);

输入d、clk rst;

输出q, qb;

qb reg问;

reg temp = 0;

always@ (posedge clk posedge rst)

开始

如果(rst = = 0)

temp = d;

其他的

temp = temp;

q = temp;

qb = ~温度;

结束

终端模块

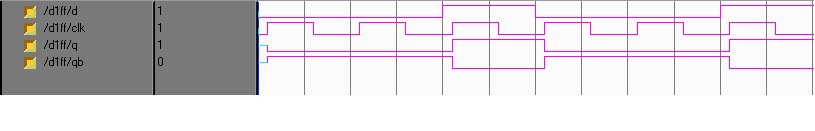

仿真结果

SR触发器的象征

下面的符号和真值表SR啪嗒啪嗒地响。

SR啪嗒啪嗒地响真值表

| rst | 公关 | Clk | 年代 | r | 问 | qb |

|---|---|---|---|---|---|---|

| 1 | X | X | X | X | 0 | 1 |

| 0 | 1 | X | X | X | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | Qb | Qbprevious |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 |

SR啪嗒啪嗒地响Verilog代码

模块srff (s, r,时钟,rst q qb);

输入s、r、clk rst;

输出q, qb;

qb reg问;

老雷格(1:0);

always@ (posedge clk posedge rst)

开始

sr = {s, r};

如果(rst = = 0)

开始

案例(sr)

2 'd1: q = 1 'b0;

2 'd2: q = 1 'b1;

2 'd3: q = 1 'b1;

默认值:开始结束

endcase

结束

其他的

开始

q = 1 'b0;

结束

qb = ~问;

结束

终端模块

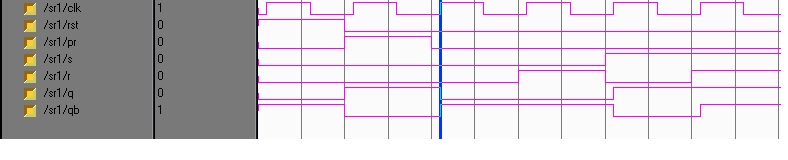

仿真结果

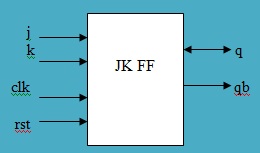

JK触发器的象征

下面的符号和真值表JK触发器。

JK触发器真值表

| Rst | Clk | J | K | 问 | Qb |

|---|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 以前的 | 状态 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | Qb | 问 |

| 1 | 没有+ ve边缘 | - - - - - - | - - - - - - | 以前的 | 状态 |

| 0 | - - - - - - | - - - - - - | - - - - - - | 0 | 1 |

JK触发器Verilog代码

模块jkff (j, k,时钟,rst q qb);

输入j、k、clk rst;

输出q, qb;

qb reg问;

reg 1:0 [] jk;

always@ (posedge clk posedge rst)

开始

jk = {j, k};

如果(rst = = 0)

开始

案例(jk)

2 'd1: q = 1 'b0;

2 'd2: q = 1 'b1;

2 'd3: q = ~ q;

默认值:开始结束

endcase

结束

其他的

q = 1 'b0;

qb = ~问;

结束

终端模块

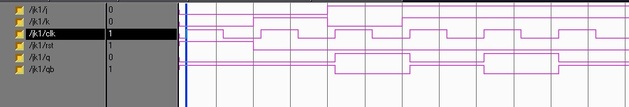

仿真结果

射频和无线教程

无线局域网802.11交流802.11广告wimax无线个域网z - waveGSMLTEUMTS蓝牙超宽频物联网卫星天线雷达