D Flipflop without reset

This page coversD Flipflop without reset与symbol,verilog code,test bench,simulation and RTL Schematic.

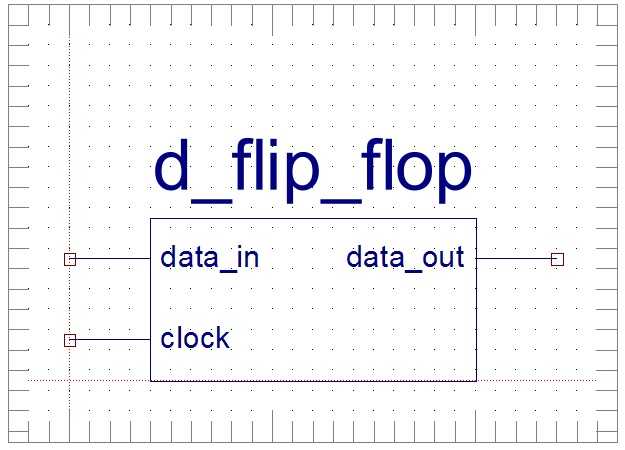

Symbol

Verilog code

module d_flip_flop(data_in,data_out,clock);

input data_in;

input clock;

output data_out;

always@(posedge clock)

begin

data_out<=data_in;

end

endmodule

input data_in;

input clock;

output data_out;

always@(posedge clock)

begin

data_out<=data_in;

end

endmodule

Test Bench

module Tb_d_flip_flop();

reg data_in;

reg clock;

wire data_out;

d_flip_flop UUT(.data_in(data_in),

.data_out(data_out),

.clock(clock));

initial begin

// Initiliase Input Stimulus

data_in = 0;

clock = 0;

end

always #100 clock=~clock;

//Stimulus

initial

begin

#100 data_in = 1'b0;

#100 data_in = 1'b1;

#600 data_in = 1'b0;

#500 data_in = 1'b1;

#200 data_in = 1'b0;

#100 $stop;

end

endmodule

reg data_in;

reg clock;

wire data_out;

d_flip_flop UUT(.data_in(data_in),

.data_out(data_out),

.clock(clock));

initial begin

// Initiliase Input Stimulus

data_in = 0;

clock = 0;

end

always #100 clock=~clock;

//Stimulus

initial

begin

#100 data_in = 1'b0;

#100 data_in = 1'b1;

#600 data_in = 1'b0;

#500 data_in = 1'b1;

#200 data_in = 1'b0;

#100 $stop;

end

endmodule

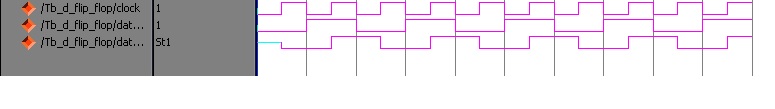

Simulation

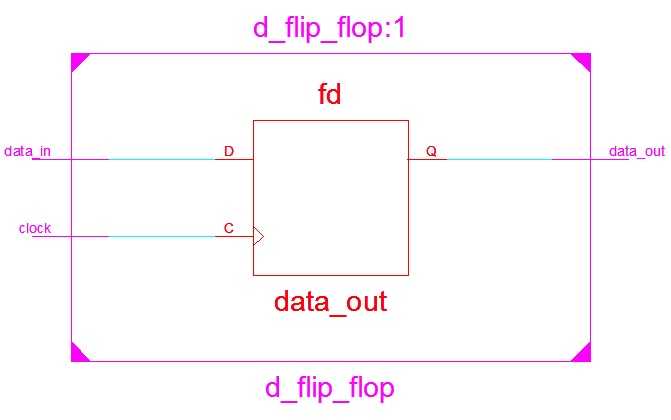

RTL Schematic

RF and Wireless tutorials

WLAN802.11ac802.11adwimaxZigbeez-waveGSMLTEUMTSBluetoothUWBIoTsatelliteAntennaRADAR