D触发器与同步复位| VERILOG代码与测试台

这D同步复位触发器涵盖符号,verilog代码,测试台,仿真和RTL原理图。介绍了用verilog代码实现D触发器的测试台。

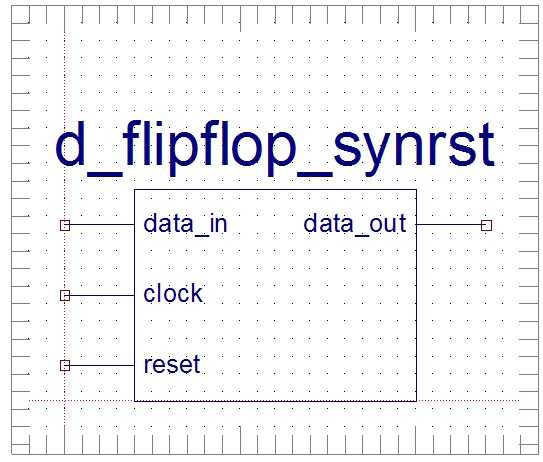

D触发器符号

D触发器Verilog代码

模块d_flipflop_synrst (data_in, data_out、时钟、复位);

输入data_in;

输入时钟、复位;

输出reg data_out;

always@ (posedge时钟)

开始

如果(重置)

data_out < = 1 'd0;

其他的

data_out < = data_in; v

endmodule

输入data_in;

输入时钟、复位;

输出reg data_out;

always@ (posedge时钟)

开始

如果(重置)

data_out < = 1 'd0;

其他的

data_out < = data_in; v

endmodule

D触发器verilog代码测试台

模块Tb_dflipflop_synrst ();

reg data_in;

reg时钟、复位;

线data_out;

d_flipflop_synrst UUT (.data_in (data_in),

.data_out (data_out),

.clock(时钟),

.reset(重置));

最初的开始

//初始化输入刺激

Data_in = 0;

时钟= 0;

重置= 0;

结束

总是#100时钟=~时钟;

/ /刺激

最初的

开始

#200 data_in = 1'b1;

Reset = 1'b1;

#200 data_in = 1'b1;

Reset = 1'b1;

#300 data_in = 1'b1;

重置= 1 'b0;

#600 data_in = 1'b0;

#500 data_in = 1'b1;

#200 data_in = 1'b0;

# 400美元停止;

结束

endmodule

reg data_in;

reg时钟、复位;

线data_out;

d_flipflop_synrst UUT (.data_in (data_in),

.data_out (data_out),

.clock(时钟),

.reset(重置));

最初的开始

//初始化输入刺激

Data_in = 0;

时钟= 0;

重置= 0;

结束

总是#100时钟=~时钟;

/ /刺激

最初的

开始

#200 data_in = 1'b1;

Reset = 1'b1;

#200 data_in = 1'b1;

Reset = 1'b1;

#300 data_in = 1'b1;

重置= 1 'b0;

#600 data_in = 1'b0;

#500 data_in = 1'b1;

#200 data_in = 1'b0;

# 400美元停止;

结束

endmodule

D触发器与同步复位仿真

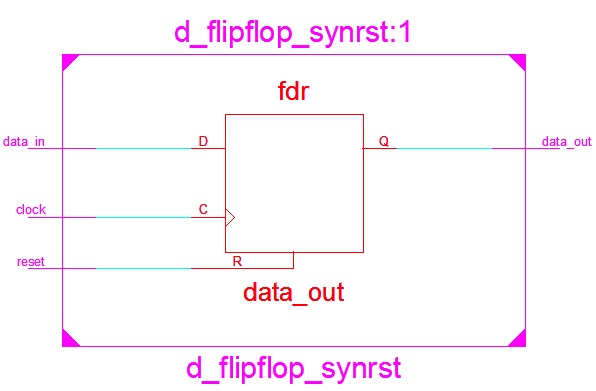

D触发器RTL示意图

射频和无线教程

无线局域网802.11交流802.11广告wimax无线个域网z - waveGSMLTEUMTS蓝牙超宽频物联网卫星天线雷达