BCD计数器HDL Verilog代码

本页verilog源代码里涵盖HDL代码BCD计数器而且灰色的计数器用verilog。

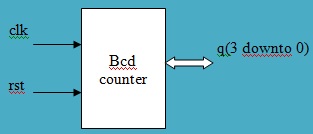

BCD计数器符号

BCD计数器真值表

| Rst | Clk | 问 |

|---|---|---|

| 1 | X | 0000 |

| 0 | 1 | 0001 |

| 0 | 1 | 0010 |

| 0 | 1 | 0011 |

| 0 | 1 | 0100 |

| 0 | 1 | 0101 |

| 0 | 1 | 0110 |

| 0 | 1 | 0111 |

| 0 | 1 | 1000 |

| 0 | 1 | 1001 |

BCD计数器Verilog代码

模块bcd(clr,clk,dir, tc, q);

输入clr、clk dir;

输出reg tc;

输出reg[3:0] q;

always@(posedge clk,posedge clr)

开始

如果(clr = = 1)

q = 4 'd0;

其他的

开始

如果(dir = = 1)

q = q + 1;

else if (dir = = 0)

q = q1;

If (dir==1 & q==4'd10)

开始

q = 4 'd0; tc = 1 'b1;

结束

Else if(dir==0 & q==4'd15)

开始

q = 1 'd9; tc = 1 'b1;

结束

其他tc = 1 'b0;

结束

结束

终端模块

BCD计数器仿真结果

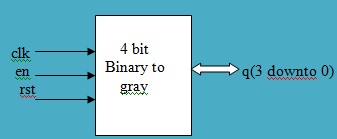

灰色计数器符号

灰色计数器真相表

| Rst | Clk | 在 | B3 | B2 | B1 | B0 | G3 | G2 | G1 | G0 |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

灰色计数器Verilog代码

模块gray(clr,clk, q);

输入clr,时钟;

输出reg[2:0] q;

reg temp = 3 'd0;

always@(posedge clk,posedge clr)

开始

如果(clr = = 0)

开始

案例(临时)

3 'd0: q = 3 'd1;

3 'd1: q = 3 'd3;

3 'd2: q = 3 'd6;

3 'd3: q = 3 'd2;

3 'd6: q = 3 'd7;

3 'd7: q = 3 'd5;

3 'd5: q = 3 'd4;

3 'd4: q = 3 'd0;

endcase

结束

其他q = 3 'd0;

结束

终端模块

射频和无线教程

无线局域网802.11交流802.11广告wimax无线个域网z - waveGSMLTEUMTS蓝牙超宽频物联网卫星天线雷达