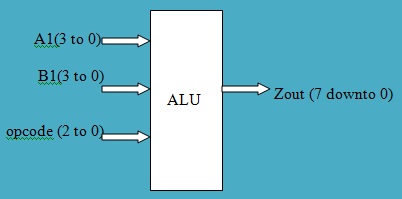

32位ALU HDL Verilog代码

本页verilog源代码里涵盖HDL代码32位ALU用verilog。这个ALU负责算术和逻辑操作。

象征

真值表

| 操作 | 操作码 | 一个 | B | Zout |

|---|---|---|---|---|

| A + B | 000 | 1111 | 0000 | 00001111 |

| a - b | 001 | 1110 | 0010 | 00001100 |

| A或B | 010 | 1111 | 1000 | 00001111 |

| A和B | 011 | 1001 | 1000 | 00001000 |

| 不是一个 | One hundred. | 1111 | 0000 | 11110000 |

| A1 * B1 | 101 | 1111 | 1111 | 11100001 |

| A和B | 110 | 1111 | 0010 | 11111101 |

| A异或B | 111 | 0000 | 0100 | 00000100 |

Verilog代码

模块ALU (a, b, s, en, y);

输入信号[3:0]a, b;

输入(握);

输入在;

输出信号[7:0]y;

reg y;

always@(a, b, s, en, y);

开始

如果(en = = 1)

开始

情况下

4�d0: y = a + b;

4�d1: y = a - b;

4�d2: y = a * b;

4 - d3: y={4 - bww, ~a};

4 - d4: y={4 - d0, (a & b)};

4�d5: y={4�d0, (a | b)};

4 - d6: y={4 - d0, (a ^ b)};

4�d7: y={4�d0, ~(a & b)};

4�d8: y={4�d0, ~(a | b)};

4 - d9: y={4 - d0, ~(a ^ b)};

默认值:begin end

结束案例

结束

其他的

y = 8�d0;

结束

终端模块

仿真结果

射频和无线教程

无线局域网802.11交流802.11广告wimax无线个域网z - waveGSMLTEUMTS蓝牙超宽频物联网卫星天线雷达