VHDL语言教程

这VHDL语言教程涵盖VHDL概念,包括实体,架构,过程,模式端口,对象类型,VHDL数据类型,操作符和示例VHDL实现。

VHDL是VHSIC硬件描述语言。VHSIC进一步缩写为超高速集成电路。VHDL是一种编程语言,用于描述数字电路的行为,范围从简单的逻辑门(几个门数)到由数百万个门组成的复杂逻辑芯片。它既可以用于设计,也可以用于编写测试工作台。

硬件描述语言(VHDL)的概念

单位/建筑

每个VHDL设计单元除了具有配置、包声明和包体外,还包括一个实体和体系结构声明。

实体定义组件的输入和输出端口信号(接口)。它给出了设计的黑盒视图。I/O端口的模式可以为在,出,inout或缓冲这取决于设计。每一个实体声明必须附有至少一份相应的文件。体系结构声明。实体定义也定义通用的参数(如果在模块中使用)。

设计的架构单元描述了设计的行为(组件的功能)。主要有三种类型的描述风格,行为描述,数据流描述和结构描述。

1.行为描述风格由几个过程语句组成。行为描述通常采用顺序的、程序性的方法。

2.数据流一般用于描述简单的逻辑块,它由并发语句组成。数据流法显示了所有的数据路径和控制信号。

3.结构方法:各种组件实例化并相互连接。主要用于元件之间的互连,每种方法都可以根据设计的需要使用。

VHDL的行为风格与C语言非常相似。它使用if-else, case, while和C中许多类似的结构,并且进程块内的语句像C中一样按顺序执行。

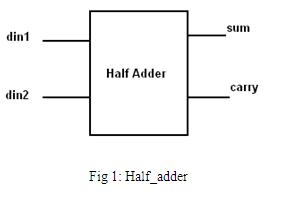

例实体:实体的主要目的是在组件的接口中声明信号。实体给出了模块的黑盒视图,即从图1中可以看到的I/O端口。

entity half_adder IS

端口(din1, din2:在std_logic;——输入

求和,执行:out std_logic);——输出

结束半加器;

体系结构

体系结构定义了电路相对于端口的功能。

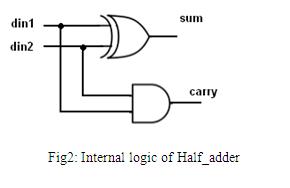

//数据流方法

half_adder的hf_arch_dataflow体系结构为

开始

Sum <= din1 xor din2;

进位<= din和din2;

结束hf_arch_dataflow

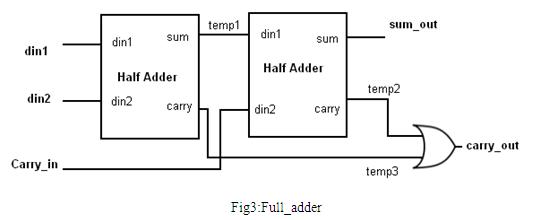

现在让我们使用这个half_adder组件来构造一个full_adder。这里我们使用结构化编码风格,下图显示了由两个半加法器组件构成的完整加法器。

实体full_adder是

Port (din1, din2, carry_in: in std_logic;——输入

Sum_out,carry_out: out std_logic);——输出

full_adder结束;

architecture full_adder_Arch of full_adder is

——组件实例化

组件half_adder

端口(din1, din2:在std_logic;——输入

求和,执行:out std_logic);——输出

结束组件;

信号temp1,temp2,temp3: std_logic;//存储中间值的信号声明

开始

组件的互连,即端口映射

H1: half_adder端口映射(din1,din2,temp1,temp3);

H2: half_加法器端口映射(temp1,carry_in,sum_out,temp2)

O1:or_gate端口映射(temp2,temp3,carry_out);——OR门的行为代码将在本节后面描述

full_adder_Arch结束;

过程

流程块是行为风格的核心。进程块中的语句是按顺序执行的。行为模型完全由流程块组成。与处理块一起传递的变量称为灵敏度列表。包含在'begin'和'end'关键字之间的语句将按顺序执行。设计中的所有其他进程块彼此并行运行。

例子:

Entity or_gate是

端口(in1,in2:在std_logic;

D_out: out std_logic);

or_gate结束;

or_gates的体系结构行为是

开始

Process (in1,in2)进程语句

开始

——与真值表比较

如果((in1='0') and (in2='0')),则

D_out <= '0';

其他的

D_out <= '1';

如果;

结束过程;

behv结束;

模式端口

接口的“端口模式”描述了数据传输的方向。IN: IN为单向端口。它可以被读取,但不能在模块内更新。OUT: OUT端口可以在模块内部更新但不能读取,它携带模块外部的信息。

INOUT: INOUT模式用于双向模式。

BUFFER:缓冲区模式用于实体内部也需要其值的输出

对象类型

信号:信号用于组件之间的互连,也用于存储临时值。信号可以在体系结构内部声明,但在体系结构外部不可用。

常量:常量是一个对象,其值在模拟过程中永远不会改变。

常数π:真正的= 3.141592653

变量:变量是创建后可以改变值的对象。

计数器:进程(x,y)

变量计数器:整数:= -1;

开始

计数器:=计数器+1;

结束过程;

VHDL数据类型

枚举类型

Boolean, ("TRUE ", "FALSE")

位类型("0","1")

字符(“b”,“f”)

字符串(“Hello”)

整数类型(375,284)

浮动类型(1.057,0.45)

标准逻辑

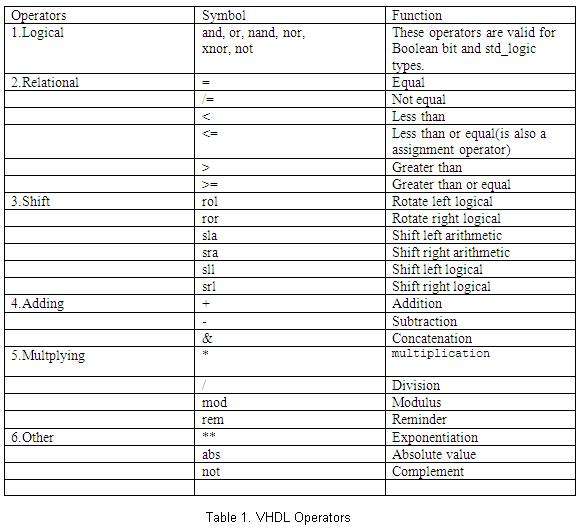

运营商

VHDL实现示例

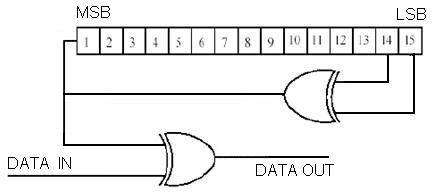

让我们实现一个在IEEE 802.16d标准中使用的简单的扰频器/随机器。按照下面所示的电路。

扰频器电路

Scarmbler VHDL代码

图书馆IEEE;

使用IEEE.STD_LOGIC_1164.ALL;

使用IEEE.STD_LOGIC_ARITH.ALL;

使用IEEE.STD_LOGIC_UNSIGNED.ALL;

实体随机器为

端口(clk:在std_logic;

重置:在std_logic;

加载:在std_logic;

种子:在std_logic_vector(14 downto 0);

Data_input: in std_logic;

Valid_input:在std_logic;

Data_output: out std_logic;

Valid_output: out std_logic

);

随机函数发生器;

的结构行为

信号shift_reg: std_logic_vector(14 downto 0);

信号valid_input1: std_logic;

信号data_input1: std_logic;

开始

过程(时钟、复位)

开始

如果reset = '1',则

Shift_reg <= (others => '0');

Valid_input1 <= '0';

Data_input1 <= '0';

Valid_output <= '0';

Data_output <= '0';

Elsif clk'event和clk = '1' then

valid_input1 < = valid_input;

data_input1 < = data_input;

如果load='1',则

Shift_reg (0) <= seed(14);

Shift_reg (1) <= seed(13);

Shift_reg (2) <= seed(12);

Shift_reg (3) <= seed(11);

Shift_reg (4) <= seed(10);

Shift_reg (5) <= seed(9);

Shift_reg (6) <= seed(8);

Shift_reg (7) <= seed(7);

Shift_reg (8) <= seed(6);

Shift_reg (9) <= seed(5);

Shift_reg (10) <= seed(4);

Shift_reg (11) <= seed(3);

Shift_reg (12) <= seed(2);

Shift_reg (13) <= seed(1);

Shift_reg (14) <= seed(0);

Elsif valid_input='1' then

Shift_reg (14) <= Shift_reg (13);

Shift_reg (13) <= Shift_reg (12);

Shift_reg (12) <= Shift_reg (11);

Shift_reg (11) <= Shift_reg (10);

Shift_reg (10) <= Shift_reg (9);

Shift_reg (9) <= Shift_reg (8);

Shift_reg (8) <= Shift_reg (7);

<= Shift_reg (6);

Shift_reg (6) <= Shift_reg (5);

Shift_reg (5) <= Shift_reg (4);

<= Shift_reg (3);

<= Shift_reg (2);

<= Shift_reg (1);

Shift_reg (1) <= Shift_reg (0);

Shift_reg (0) <= Shift_reg (13) xor Shift_reg (14);

如果;

如果valid_input1 = '1',则

xor data_input1 <= shift_reg(0);

Valid_output <= '1';

其他的

Data_output <= '0';

Valid_output <= '0';

如果;

如果;

结束过程;

端行为;

有用的链接到VHDL代码

参考以下以及左侧面板上提到的有用的VHDL代码的链接。

D触发器

T触发器

读写RAM

4 x1 MUX

4位二进制计数器

Radix4蝴蝶

16 qam调制

2bit并行串行

射频和无线教程

无线局域网802.11交流802.11广告wimax无线个域网z - waveGSMLTEUMTS蓝牙超宽频物联网卫星天线雷达