ARM寄存器集,处理器模型和流水线概念

本ARM教程涵盖了ARM寄存器集、处理器模型和流水线概念。有关其他ARM教程内容,请参阅以下页面。

ARM教程page1

ARM教程第二页

ARM教程第3页

ARM教程第4页

ARM教程第5页

ARM教程第6页

寄存器数:总共37个寄存器。20(存入银行)始终不可见。所有模式下最小17可见。16个通用,1个相关状态。

存储寄存器:每种模式都有一组额外的寄存器,称为存储寄存器。每当模式发生变化时,就交换存储寄存器。

R13 - sp;在当前处理器模式下保持堆栈头。

R14 - LR(在调用子例程时指向返回地址)

R15 - pc。程序计数器。包含处理器要获取的下一条指令的地址。

部门登记

| 用户系统 | FIQ | 硬中断请求优先级别 | SVC | Undef | 中止 |

|---|---|---|---|---|---|

| 罗依 | 罗依 | 罗依 | 罗依 | 罗依 | 罗依 |

| r1 | r1 | r1 | r1 | r1 | r1 |

| r2 | r2 | r2 | r2 | r2 | r2 |

| r3 | r3 | r3 | r3 | r3 | r3 |

| r4 | r4 | r4 | r4 | r4 | r4 |

| r5 | r5 | r5 | r5 | r5 | r5 |

| r6 | r6 | r6 | r6 | r6 | r6 |

| r7 | r7 | r7 | r7 | r7 | r7 |

| r8 | r8_fiq | r8 | r8 | r8 | r8 |

| r9机型 | r9_fiq | r9机型 | r9机型 | r9机型 | r9机型 |

| r10 | r10_fiq | r10 | r10 | r10 | r10 |

| r11 | r11_fiq | r11 | r11 | r11 | r11 |

| r12 | r12_fiq | r12 | r12 | r12 | r12 |

| r13 / SP | r13_fiq | r13_irq | r13_svc | r13_undef | r13_abort |

| r14 / LR | r14_fiq | r14_irq | r14_svc | r14_undef | r14_abort |

| r15 /电脑 | r15 /电脑 | r15 /电脑 | r15 /电脑 | r15 /电脑 | r15 /电脑 |

| SPSR | - | - | - | - | - |

| - | SPSR_fiq | SPSR_irq | SPSR_SVC | SPSR_undef | SPSR_abort |

ARM处理器模式:

中止、FIQ、IRQ、监督、系统、用户、未定义是处理器模式。

Abort:内存读写失败。

FIQ、IRQ:与ARM中的中断有关。

Supervisor:重置后,通常是内核运行的模式。

系统模式:用户模式的特殊版本,允许完全访问CPSR。

未定义模式:当遇到未定义指令时进入。

模式可以是特权模式(所有减去用户模式)或非特权模式(用户模式)。

确定哪些寄存器是活动的,以及谁拥有对CPSR的访问权限。

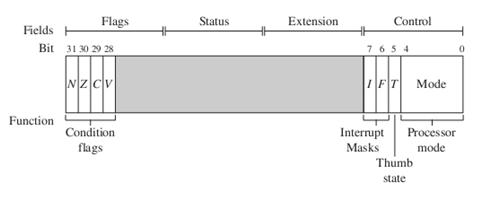

特权模式允许对CPSR进行完全读写访问。

非特权模式只允许对CPSR模式字段进行读访问,但允许对条件标志进行读/写访问。

表2,ARM条件标志

| 国旗 | 国旗的名字 | 时设置 |

|---|---|---|

| 问 | 饱和 | 结果导致溢出和/或饱和 |

| V | 溢出 | 结果将导致有符号溢出 |

| C | 携带 | 结果导致无符号进位 |

| Z | 零 | 结果为零,常用于表示相等 |

| N | 负 | 结果的第31位是二进制1 |

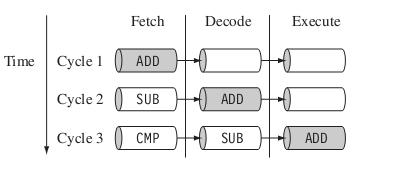

ARM管道特性

正如我们所知,更多的阶段意味着更高的频率,更高的系统延迟。

管道与PC关系:

在ARM状态下,

PC =当前指令加8。

在拇指模式下,

PC =当前指令+4

其他特征:在遗留的ARM核心中,执行分支导致管道刷新。分支预测用于减少管线冲平的影响。

在执行阶段的指令被服务之前,中断不会被服务。在中断时刷新管道中的指令。