卷积编码

本页描述了卷积编码器的示例,并提到了卷积编码的伪代码。卷积编码示例采用码率、约束长度、生成器多项式进行实现。

让我们按照以下规范来理解卷积编码器的例子。

卷积编码器(3,1,4)规格

编码率:1/3

约束长度:5

输出位长:3

消息位长:1

最大内存顺序/个数。内存元素= 4

生成器多项式:25 (8),33 (8),37 (8)

描述:

前向纠错的目的是通过向通过信道传输的数据中添加一些精心设计的冗余信息来提高信道的容量。添加冗余信息的过程称为信道编码。卷积码对串行数据进行操作,每次操作一位或几位。

带维特比解码的卷积编码是一种FEC技术,特别适用于主要由加性高斯白噪声(AWGN)破坏传输信号的信道。

卷积码通常使用两个参数来描述:

编码速率

约束长度。

码率= k/n,表示为进入卷积编码器(k)的比特数与卷积编码器(n)在给定编码器周期中输出的通道符号数的比率。

约束长度参数K表示卷积编码器的“长度”,即有多少K位级可用于输入产生输出符号的组合逻辑。

与K密切相关的是参数m,它表示输入位在卷积编码器的输入中首次出现后,被保留并用于编码的编码器周期的数量。m参数可以被认为是编码器的内存长度。我们关注速率为1/3的卷积码。

维特比译码的优点是译码时间固定。它非常适合硬件解码器实现。但它的计算需求作为约束长度的函数呈指数增长,因此在实践中通常限制约束长度K = 9或更小。

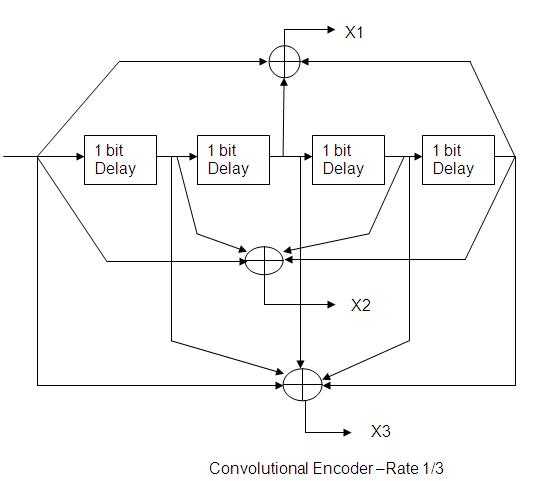

输入的原始二进制数据由二进制卷积编码器编码,其原生速率为1/3,约束长度为5,并使用以下生成器多项式码来推导其三个码位(X1, X2, X3):

25 (8), 33 (8), 37 (8)

卷积编码器的例子

卷积编码器的生成器部分如下图所示。

伪代码:

对数据进行卷积编码是使用移位寄存器和相关的组合逻辑来完成的,该组合逻辑执行模二相加。(移位寄存器只是一连串的触发器,其中第n个触发器的输出与第(n+1)个触发器的输入绑定在一起。每次时钟的活动边发生时,触发器的输入被打卡到输出,因此数据被转移到一个阶段。

八进制数(25)8(33)8(37)8表示代码生成器多项式,当以二进制(10101)读取时2, (11011)2和(11111)2对应于移位寄存器连接到上模和下模两个加法器,分别如上图所示。在设计卷积编码器时,遵循以下步骤。

1)在重置时初始化内存寄存器为零

M1 =0, m2=0, m3=0, m4=0

2)将输入的位存储在内存寄存器m_in中。

M_in = data_in

3)当输入位到达并且输入的数据有效后,操作开始,输出计算为

X1 = m_in + m2 + m4;

X2 = m_in + m1 + m3 + m4;

X3 = m_in + m1 +m2 +m3+m4;

4)换挡操作

m4 =立方米;

m3 =平方米;

m2 = 1;

m1 = m_in;

5)步骤2、3和4重复输入数据位的长度

MATLAB源代码

VHDL源代码

对于K=7,速率=1/2,G1=171(八进制),G2 = 133(八进制),检查VHDL代码在以下页面:

卷积编码器

相关链接

前向纠错本页面描述了前向纠错及其应用,并提到了不同的前向纠错技术。

涡轮编码器-本页涵盖了CTC编码器或卷积Turbo编码器技术的速率1 × 3的例子,用于前向纠错。

RS编码器-本页涵盖RS编码器,即芦苇所罗门编码基础与示例。

儿童权利公约-本页涵盖CRC或循环冗余检查。